In the coming posts, we will learn circuits implemented with both combinational and sequential circuits. In the waveform, Cout (output carrry) is shown by MSB of the “oc” register.

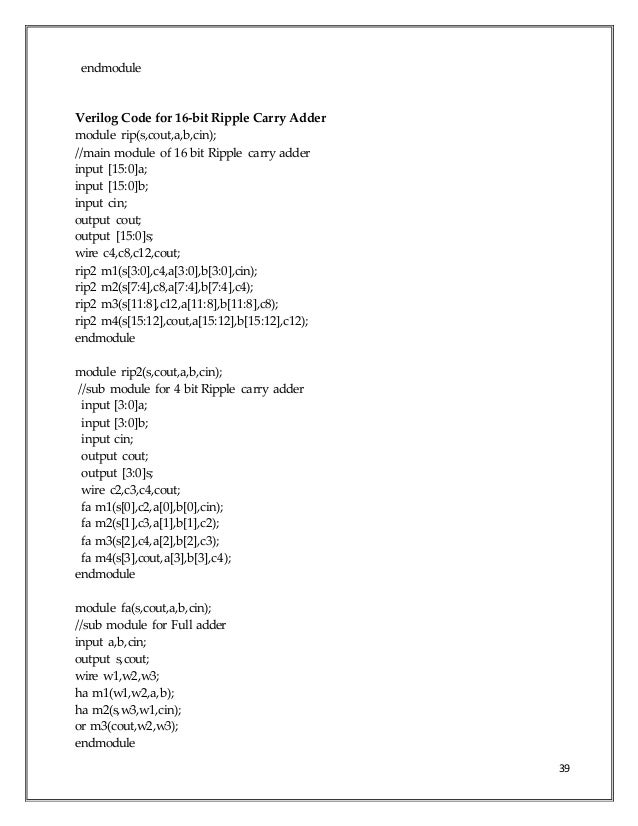

You can use Karnaugh Map to implement the logic given in above table using gates.Ĭ= (A and B) or (B and Cin) or (Cin and A)įor N bit Parallel Adder, we need N Full Adder modules cascaded in the manner shown In the above figure.Īssign o = (~ic & ((a & ~b) | (~a & b)) ) | (ic & ~((a & ~b) | (~a & b)) ) Īssign oc = (a & b) | (b & ic) | (ic & a) įulladder fa1(in1,in2,ic,out,oc) įulladder fa2(in1,in2,oc,out,oc) įulladder fa3(in1,in2,oc,out,oc) įulladder fa4(in1,in2,oc,out,oc) Truth Table for Full Adder implementation will be: How do I code a full adder in Verilog module fulladder ( input 3:0 a, input 3:0 b, input cin, output reg cout, output reg 3:0 sum) always (a. C is carry generated due to the addition of A and B. Let A and B are two single bit inputs and Cin is the input carry. The sum is the sum of bit A and B. I discovered this by looking at the waveforms for the. Then we use this Full Adder module N times to implement Parallel Adder of N bits. Here is the Verilog code for the Full Adder: module halfadder(x,y,S,C) input x,y output S,C xor G1(S,x,y) and G2(C,x,y) endmodule module fulladder(x,y,z,S,C) input x,y,z output S,C wire S1,C1,C2 halfadder HA1(S1,C1,x,y) halfadder HA2(S,C2,S1,z) or G3(C,C1,C2) endmodule. Parallel Adder is a combinational circuit which is used to add two N-bit binary numbers.We use Full Adder module to add two single bit binary numbers with an initial input carry.

#Verilog code for full adder software#

Let’s discuss it step by step as follows. The results include successful compilation of the VHDL code in the Xilinx software along with the waveforms that prove the legality of the truth table.

#Verilog code for full adder how to#

Addition of two binary numbers is an important concept which everyone must know how to implement. Write a Verilog HDL to design a Full Adder. The code discussed in this post will be used in future posts.

In this post, we will implement a 4-bit Parallel Adder using Full Adder module.

0 kommentar(er)

0 kommentar(er)